УДК 004.383; 681.518.5

# УМЕНЬШЕНИЕ ВРЕМЕНИ ТЕСТИРОВАНИЯ FLASH-ПАМЯТИ ПРИ ПРОГРАММИРОВАНИИ С ИСПОЛЬЗОВАНИЕМ ГРАНИЧНОГО СКАНИРОВАНИЯ

### Н.В. Сильянов

Российский федеральный ядерный центр — Всероссийский научно-исследовательский институт экспериментальной физики

Россия, 603952, Нижний Новгород, Бокс № 486, Тропинина ул., 47

E-mail: silianov@mail.ru

### Л.С. Ломакина

Нижегородский государственный технический университет им. Р.Е. Алексеева Россия, 603950, Нижний Новгород, ГСП-41, Минина ул., 24 E-mail: llomakina@list.ru

Ключевые слова: тестирование памяти, граничное сканирование.

Аннотация: В статье описана разработка вспомогательного обеспечения, требуемого для тестирования оперативной и Flash-памяти до программирования и запуска микропроцессорного устройства. Эти операции на начальной стадии после монтажа могут быть безопасно проведены с использованием технологии граничного сканирования. Для такого тестирования разработаны методология и соответствующее оборудование. Описано специализированное программное обеспечение для управления сигналами программирования и настройки их временных параметров. Приведены осциллограммы данных сигналов. Даны рекомендации для достижения приемлемого для массового производства времени тестирования и программирования Flash-памяти.

### 1. Введение

Большинство современных систем автоматического управления содержат микропроцессорные устройства с оперативной и перепрограммируемой (Flash) памятью. Требуется около 50-60 цепей для соединения микропроцессора с памятью с 32-битной шириной шины. При использовании четырех корпусов микросхем памяти для обеспечения требуемой информационной емкости существует порядка 450-540 контактов или контактных площадок, которые могут быть причиной таких неисправностей, как обрывы и короткие замыкания. Эти неисправности должны быть обнаружены до поиска функциональных неисправностей [1]. Как правило, наиболее часто встречающейся структурной неисправностью является короткое замыкание [2].

Для решения данных проблем современные микропроцессоры и микроконтроллеры поддерживают технологию граничного сканирования. Эта технология описывается стандартом IEEE Std. 1149.1 [3]. Обобщенная структура интегральной микросхемы с поддержкой этого стандарта показана в [1]. Микросхема содержит дополнительную тестовую логику. Регистр граничного сканирования (BSR) помещается на границе микросхемы между контактами ввода-вывода и системной логикой (ядром). Регистр

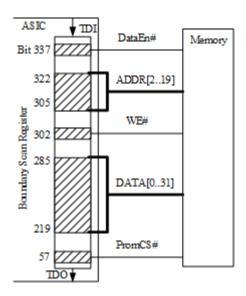

BSR позволяет захватывать текущее состояния контактов микросхемы или устанавливать их в новое требуемое состояние. Длина регистра граничного сканирования определяется количеством контактов и их типом (входные, выходные, двунаправленные). Пример регистра для СБИС 5890ВЕ1Т показан на рис. 1.

Рис. 1. Соответствие битов регистра граничного сканирования сигналам шины памяти.

Для формирования временных диаграмм пересылок памяти необходимо управлять битами регистра BSR, отвечающими за адреса, данные и сигналы управления шины. Тестируемое устройство содержит СБИС 5890ВЕ1Т в качестве микропроцессора, БИС 1636РР1АУ в качестве Flash-памяти и БИС 1657РУ1У в качестве оперативной памяти. Циклы чтения на шине памяти как для ОЗУ, так и для Flash-памяти, являются тривиальными. Циклы записи для Flash-памяти должны соответствовать фиксированной специальной последовательности служебных циклов по определенным адресам.

# 2. Разработка диагностического обеспечения

### 2.1. Разработка методики исследований

Для сопряжения дополнительной логики граничного сканирования с управляющей ЭВМ, контролирующей все процессы тестируемого устройства, необходимы адаптер порта тестового доступа и соответствующее программное обеспечение. Основной причиной для разработки собственного диагностического обеспечения является необходимость изменения служебных циклов и настройки времен предустановки и удержания управляющих сигналов выборки кристалла и разрешения записи. Методика исследований для тестирования и программирования основана на загрузке бинарного файла в память, чтении содержимого памяти и его сравнении с загруженным. Тестовые двоичные файлы с чередованием нулей и единиц (т.е. с шестнадцатеричными кодами 0х5555555 и 0хАААААА) могут быть приготовлены заранее для проверки отсутствия дефектов памяти «короткое перед шины типа замыкание» программированием целевого файла.

Для записи чистой Flash-памяти есть два способа:

• программировать каждую ячейку со специальным механизмом контроля (бит D7);

- программировать ячейку без механизма контроля статуса программирования, но с последующей верификацией.

- Также можно программировать память:

- записывать и считывать ячейку за ячейкой;

- записывать весь объем, а потом считывать его. Запись ячейки может быть выполнена двумя способами:

- с помощью 4-цикловой командной последовательности "Program";

- с помощью 2-цикловой командной последовательности "Unlock Bypass Program".

В соответствии со спецификацией на микросхему 1636PP1AУ, цикл команд типа "Unlock Bypass Program" должен предваряться последовательностью "Unlock Bypass", а последняя команда должна завершаться циклом шины "Unlock Bypass Reset". Механизм контроля программирования путем чтения бита D7 может быть опущен. Если ячейка памяти не прошилась, необходимо ее повторное программирование.

Для программирования с использованием граничного сканирования необходим адаптер, который сопрягает интерфейс шины USB с портом тестового доступа. Основным компонентом схемы является микросхема DD1 FT232H [4]. Для эмуляции сигналов управления TAP-портом «JTAG» эта микросхема должна использоваться в режиме Multi-Protocol Synchronous Serial Engine (MPSSE) [5].

# 2.2. Разработка программного обеспечения для управления тестированием и программированием памяти

Управление микросхемой FT232H реализуется через интерфейс USB с помощью программного обеспечения управляющей ЭВМ на основе драйвера FTDIBUS.SYS с использованием динамической библиотеки FTD2XX.dll [6].

Команды MPSSE обрабатываются микросхемой FT232H для обмена данными и генерации сигналов TAP-порта [7]. Обычно пакет данных MPSSE содержит код операции, длину сообщения (в байтах или битах) и непосредственно данные. После того как пакет MPSSE сформирован, запускается передача последовательностей импульсов сигналов TAP от эмулятора к СБИС.

В штатном режиме работы временные параметры сигналов управления памятью (такие как время предустановки, время удержания, время программирования байта и др.) обеспечиваются с помощью контроллера внешней памяти СБИС. Однако, при использовании на начальной стадии тестирования технологии граничного сканирования функциональные блоки микросхемы изолированы от контактов вводавывода. Также, частота работы шины памяти гораздо ниже, чем в штатном режиме. Поэтому временные параметры сигналов выбора микросхемы и управления записью гораздо больше, чем минимально допустимые.

Для уменьшения общего времени процесса необходимо прежде всего изменять величину времени цикла программирования байта. После этого другие временные параметры также могут подстраиваться.

### 2.3. Экспериментальные исследования

В процессе разработки программного обеспечения было отмечено, что скорость программирования Flash-памяти ограничивается параметром "Latency Timer" с минимально возможным значением 2 мс. Это время задержки для USB-транзакций между эмулятором и управляющей ЭВМ. Для микросхемы FT232H это время не может быть уменьшено. В таком случае программирование памяти объемом 2 Мбайт будет занимать более 50 минут, что является неприемлемым. Несмотря на это, существует возможность передавать больше данных за одну USB-транзакцию, используя

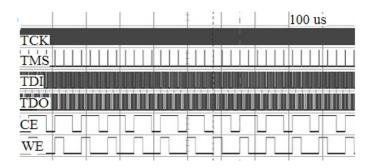

встроенный в микросхему FT232H буфер размером 64 Кбайт. Это позволяет увеличить скорость программирования приблизительно в 20 раз. Транзакции сигналов управления TAP-портом и управления памятью CE-WE без использования и с использованием буферизации показаны на рис. 2 и 3 соответственно. Общее время программирования файла размером 2 Мбайт для различных способов записи приведено в таблице 1.

| TCK |  |  |  | 2 ms |  |

|-----|--|--|--|------|--|

| TMS |  |  |  |      |  |

| TDI |  |  |  |      |  |

| TDO |  |  |  |      |  |

| CE  |  |  |  |      |  |

| WE  |  |  |  |      |  |

Рис. 2. Транзакции сигналов управления без использования буферизации.

Рис. 3. Транзакции сигналов управления с использованием буферизации.

**Таблица 1.** Число повторных обращений и общее время программирования для различных способов записи.

| Способ программирования      | Задержка               | Число повторных | Общее  |

|------------------------------|------------------------|-----------------|--------|

| 2 2 2                        | программирования байта | записей         | время  |

| 4-цикловая командная         | 1 мс                   | 926             | 14 мин |

| последовательность "Program" |                        |                 | 45 c   |

|                              | 200 мкс                | 2398            | 7 мин  |

|                              |                        |                 | 05 с   |

|                              | 10 мкс                 | 012             | 5 мин  |

|                              |                        |                 | 05 с   |

|                              | 0                      | 920             | 5 мин  |

|                              |                        |                 | 40 c   |

| 2-цикловая командная         | 1 мс                   | 0104            | 12 мин |

| последовательность "Unlock   |                        |                 | 20 c   |

| Bypass Program"              | 200 мкс                | 1069            | 4 мин  |

|                              |                        |                 | 55 c   |

|                              | 10 мкс                 | 239             | 3 мин  |

|                              |                        |                 | 05 с   |

|                              | 0                      | 4114            | 2 мин  |

|                              |                        |                 | 55 c   |

| Последовательность без       | 0                      | 0               | 1 мин  |

| служебных циклов для ОЗУ     |                        |                 | 35 c   |

### 3. Заключение

В результате проведенных исследований можно сформировать набор практических правил для уменьшения времени тестирования и программирования Flash-памяти до приемлемых для массового производства значений:

- помещать пакеты TAP-транзакций во внутренний буфер управляющей микросхемы (например, FT232H);

- помещать пакеты в буфер так, чтобы не происходило нарушений служебных циклов на границе окончания буфера (без разделения командных последовательностей записи);

- тестировать ОЗУ пока Flash-память стерта, чтобы предотвратить повреждение данных из-за вмешательства системной логики, когда ТАР-контроллер отпускает шину и возможно исполнение каких-либо инструкций процессора;

- записывать и считывать весь объем памяти, а не последовательно ячейку за ячейкой;

- программировать ячейку Flash-памяти без механизма контроля статуса, но с чтением, верификацией и повторной записью, если потребуется (если какие-либо ячейки оказались не запрограммированы);

- использовать командную последовательность "Unlock Bypass Program" вместо "Program";

- установить для диагностического обеспечения параметр времени программирования байта на уровне 10 мкс.

## Список литературы

- 1. Городецкий А., Курилан Л. Введение в технологию граничного сканирования // Производство электроники: технологии, оборудование, материалы. 2007. № 5. С. 1-5.

- 2. Сперанский Д.В., Скобцов Ю.А., Скобцов В.Ю. Моделирование, тестирование и диагностика цифровых устройств. М.: ИНТУИТ, 2016. 535 с.

- 3. IEEE Std 1149.1-2013. IEEE Standard for Test Access Port and Boundary-Scan Architecture. https://ieeexplore.ieee.org/document/938734 (дата обращения 27.12.2023).

- 4. FT232H Single Channel Hi-Speed USB to Multipurpose UART/FIFO IC: Datasheet FT\_000288. https://ftdichip.com/wp-content/uploads/2020/07/DS\_FT232H.pdf (дата обращения 27.12.2023).

- 5. FTDI MPSSE Basics: Application Note AN\_135. https://ftdichip.com/Support/Documents/AppNotes/AN\_135\_MPSSE\_Basics.pdf (дата обращения 27.12.2023).

- 6. Software Application Development D2XX Programmer's Guide: FT\_000071. https://ftdichip.com/wp-content/uploads/2020/08/D2XX Programmers GuideFT 000071.pdf (дата обращения 27.12.2023).

- 7. Command Processor for MPSSE and MCU Host Bus Emulation Modes: Application Note AN\_108. https://ftdichip.com/Documents/AppNotes/AN\_108\_Command\_Processor\_for\_MPSSE\_and\_MCU\_Host\_B us Emulation Modes.pdf (дата обращения 27.12.2023).